# Universal Logic Gate: ENOR

## **Rajesh Fithelis**

Department of Software Engineering, BlackSun Information Support Services, North Street, Marthandam, Kanyakumari District, Tamil Nadu, India, Postal Code: 641012. email: rajeshf@live.com

Abstract. This paper discusses about additional (derived) universal logic gate useful in the binary circuit, namely ENOR (Emergency NOR) on the base of NOT gate; The proposed logic gates are differ from the existing universal gates; to handle the must/emergency conditions, such as after starting any process the condition is to stop a process at any scenario until the process get completed. The proposed gate was well defined and simulated with well-defined truth table. The simulation result shows that the working principle of ENOR was well defined with truth tables, algebraic formula and efficiency.

Keywords: ENOR, NOR gate, OR gate, emergency gate, NOT gate;

## I. Introduction

In electronics, logic gates are the fundamental building blocks of all digital systems. All the existing basic logic gates or derived logic gates were designed to produce a logical/binary out; in some cases to convert all values to produce the desired binary out is not possible by a single gate; for example to convert all binary values to ZERO or ONE. The proposed ENOR logic gate can be used based on the requirements to get the desired binary out [1-20].

## II. NOT gate

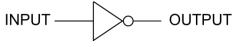

NOT gate has one-input and one-output. It is a logic circuit whose output is always the complement of the input. Fig.1 indicates the logic symbol and truth table of NOT gate along with simple implementation using switches.

Fig.1: NOT gate graphic symbol

The purpose of inverter is to change one logic level to opposite level. The LOW level at input produces a HIGH level and vice versa. In terms of bits, it changes a 0 to a 1 and a 1 to 0.

## **III. ENOR Logic Gate**

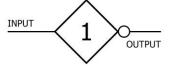

In digital logic, a ENOR or ENOR gate is a logic gate which converts its input to 1 (ONE) or HIGH. The main purpose of a ENOR is to convert any input to HIGH. ENOR has one input and one output; its output always HIGH; simply, ENOR is a very basic active device that generates 1 as output; ENOR gate symbolically shown in Fig. 2.

Fig.2: Proposed ENOR gate graphic symbol

## A. Truth Table

The Truth Table shows the values of the circuit output for all input values or the Truth Table shows a logic circuit's output response to all of the input combinations.

| INPUT (A) | OUTPUT (F)<br>$F = \overline{A} + A$ |

|-----------|--------------------------------------|

| 0         | 1                                    |

| 1         | 1                                    |

Table.1: ENOR gate Truth Table

#### i. Algebraic Function

The process of converting control objectives into a ladder logic program requires structured thought. Boolean algebra provides the formula needed to analyze and design these systems. The algebraic formula of the proposed ENOR gate is below. Logic gates are electronic circuits that implement the basic functions of Boolean Algebra.

| Combinational Analysis                    |        |

|-------------------------------------------|--------|

| File Edit Project Simulate Window Help    |        |

| Inputs Outputs Table Expression Minimized |        |

| <b>a x</b><br>0 1<br>1 1                  | ~<br>~ |

| Build Circuit                             |        |

Fig.3: ENOR gate Truth Table (LOGISIM, Ver: 2.7.1)

Boolean Algebra is the mathematical foundation of digital circuits. Boolean Algebra specifies the relationship between Boolean variables which is used to design combinational logic circuits using Logic Gates.

----- (1)

$F = \overline{A} + A$

Combinational Analysis

File Edit Project Simulate Window Help

Inputs Outputs Table Expression Minimized

Output: x

a + a

a

Clear Revert Enter

Build Circuit

Fig.4: ENOR expression (LOGISIM, Ver: 2.7.1)

| D Combinational Analysis                  | _ 0 | 23 |

|-------------------------------------------|-----|----|

| File Edit Project Simulate Window Help    |     |    |

| Inputs Outputs Table Expression Minimized |     |    |

|                                           |     | •  |

|                                           |     |    |

| Output: x 👻                               |     |    |

| Format: Sum of products 👻                 |     |    |

|                                           |     |    |

| a                                         |     |    |

| 0 1                                       |     |    |

| 1 1                                       |     |    |

| 1                                         |     |    |

| 1                                         |     |    |

| Set As Expression                         |     |    |

|                                           |     |    |

|                                           |     | -  |

| Build Circuit                             |     |    |

|                                           |     |    |

Fig.5: ENOR gate Truth table by 'Sum of Product'

| D Combinational Analysis                  | _ 0 | 23  |

|-------------------------------------------|-----|-----|

| File Edit Project Simulate Window Help    |     |     |

| Inputs Outputs Table Expression Minimized |     |     |

|                                           |     | •   |

|                                           |     |     |

| Output: x 👻                               |     |     |

|                                           |     |     |

| Format: Product of sums 👻                 |     |     |

| a                                         |     |     |

| 0 1                                       |     |     |

| 1 1                                       |     |     |

|                                           |     |     |

| 1                                         |     |     |

| Set As Expression                         |     |     |

| SEL AS EXPRESSION                         |     |     |

|                                           |     | -   |

|                                           |     | · · |

| Build Circuit                             |     |     |

Fig.6: ENOR gate Truth table by 'Product of Sum'

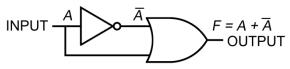

## ii. Detailed Graphic Symbol

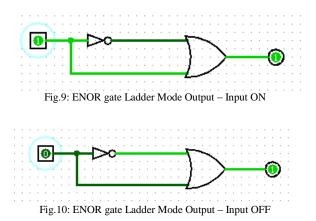

The ENOR is a combination of both NOT and OR gates; so that the output of NOT gate is fed as one input of the OR gate and for another input it shares the NOT gate input to produces the output. Fig.3 shows the detailed working principle.

Fig.7: ENOR gate detailed graphic symbol

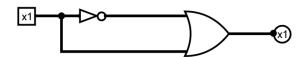

Fig.8: ENOR gate structural output of LOGISIM

## **III. Result & Discussion**

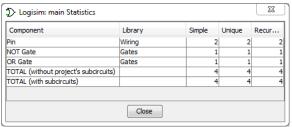

The well-defined truth table, algebraic formula and detailed working principle shows the gate perfectness. The gates where simulated under LOGISIM 2.7.1(version) on different modes with following specifications.

Fig.11: ENOR gate Statistics

## **Device Report**

- LOGISIM V 2.7.1

- SA2 Type of the PLC

- Tick Frequency 1Hz

- Ladder Diagram- High level language

# V. Conclusion

The proposed ENOR gate was simulated and tested; the clock output, the well-defined algebraic equation and Truth table shows the clear working principal of the gate. This gate can be used for various purposes such as to minimize the complicated circuits, as a switch etc... In the digital electronic as an addition to improve the technology.

The ENOR gate is a basic digital logic gate that implements logical conjunction - it behaves according to the truth table to the right. A HIGH output (1) results for all the inputs to the ENOR gate. If none or not all inputs to the ENOR gate are HIGH or LOW, a HIGH output results.

## References

- J. A. Roese, "Interframe cosine transform image coding", IEEE Trans. Commun., vol. COM-25, pp. 1329-1338, Nov. 1977.

- Jaeger, Microelectronic Circuit Design, McGraw-Hill 1997, ISBN 0-07-032482-4, pp. 226–233

- [3] Tinder, Richard F. (2000). Engineering digital design: Revised Second Edition. pp. 317– 319. ISBN 0-12-691295-5. Retrieved 2008-07-04.

- [4] Rowe, Jim. "Circuit Logic Why and How" (December 1966). Electronics Australia.

- [5] Nylan, Michael (2001). The Five "Confucian" Classics. Yale University Press. pp. 204– 206. ISBN 978-0-300-08185-5. Retrieved 8 June 2010.

- [6] Perkins, Franklin. Leibniz and China: A Commerce of Light. Cambridge: Cambridge University Press, 2004. p 117. Print.

- [7] Peirce, C. S., "Letter, Peirce to A. Marquand", dated 1886, Writings of Charles S. Peirce, v. 5, 1993, pp. 421–23. See Burks, Arthur W., "Review: Charles S. Peirce, The new elements of mathematics", Bulletin of the American Mathematical Society v. 84, n. 5 (1978), pp. 913–18, see 917. PDF Eprint.

- [8] History of Research on Switching Theory in Japan, IEEJ Transactions on Fundamentals and Materials, Vol. 124 (2004) No. 8, pp. 720– 726, Institute of Electrical Engineers of Japan

- [9] Switching Theory/Relay Circuit Network Theory/Theory of Logical Mathematics, IPSJ

Computer Museum, Information Processing Society of Japan

- [10] Radomir S. Stanković (University of Niš), Jaakko T. Astola (Tampere University of Technology), Mark G. Karpovsky (Boston University), Some Historical Remarks on Switching Theory, 2007, DOI 10.1.1.66.1248

- [11] Radomir S. Stanković, Jaakko Astola (2008), Reprints from the Early Days of Information Sciences: TICSP Series On the Contributions of Akira Nakashima to Switching Theory, TICSP Series #40, Tampere International Center for Signal Processing, Tampere University of Technology

- [12] "Who Invented the Transistor?". Computer History Museum. 4 December 2013. Retrieved 20 July 2019.

- [13] "1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated". The Silicon Engine: A Timeline of Semiconductors in Computers. Computer History Museum. Retrieved August 31, 2019.

- [14] Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. pp. 321–3. ISBN 9783540342588.

- [15] "1963: Complementary MOS Circuit Configuration is Invented". Computer History Museum. Retrieved 6 July 2019.

- [16] Overview of IEEE Standard 91-1984

Explanation of Logic Symbols, Doc. No. SDYZ001A, Texas Instruments Semiconductor Group, 1996

- [17] Peirce, C. S. (manuscript winter of 1880–81), "A Boolian Algebra with One Constant", published 1933 in Collected Papers v. 4, paragraphs 12–20. Reprinted 1989 in Writings of Charles S. Peirce v. 4, pp. 218–21, Google [1]. See Roberts, Don D. (2009), The Existential Graphs of Charles S. Peirce, p. 131.

- [18] Hans Kleine Büning; Theodor Lettmann (1999). Propositional logic: deduction and algorithms. Cambridge University Press. p. 2. ISBN 978-0-521-63017-7.

- [19] John Bird (2007). Engineering mathematics. Newnes. p. 532. ISBN 978-0-7506-8555-9.

- [20] Mechanical Logic gates (focused on molecular scale)

- [21] DNA Logic gates Archived 2010-06-18 at the Wayback Machine.